- Getting Started Install Ghidra

MDK-ARM

- ▲ Memory Requirements

Linker Map File Ghidra

- Examining Object Code and Control Flow Ignoring Control Flow Simple Control Flow Complex Control Flow

- Examining Function Calling Behavior

Linker Static Call Graph

Ghidra

Source Code vs. Decompiled Code

Scroll down to the last two sections in the map file to determine the following values in bytes (not kB).

- 1. What is the **Total ROM Size** in bytes?

- 2. What is the **Total RW Size** in bytes? This is the total RAM required.

- 3. What is the size of RW Data in RAM in bytes? Note this is uncompressed RW Data (in Grand Totals).

- 4. What is the size of RW Data in ROM in bytes? Note this is compressed RW Data (in ELF Image Totals (compressed)).

- 5. How much **ROM** space in bytes is used for code?

- 6. How much of that **ROM** space is used for included data (e.g. literal pools, listed as ".inc data")?

\_\_\_\_\_\_

| Code (i | nc. data) | RO Data | RW Data | ZI Data | Debug  |                               |

|---------|-----------|---------|---------|---------|--------|-------------------------------|

| 20020   | 1352      | 4832    | 3 1068  | 9480    | 217705 | Grand Totals                  |

| 20020   | 1352      | 4832    | 4 312   | 9480    | 217705 | ELF Image Totals (compressed) |

| 5 20020 | 6 1352    | 4832    | 312     | 0       | 0      | ROM Totals                    |

------

```

Total RO Size (Code + RO Data) 24852 ( 24.27kB)

Total RW Size (RW Data + ZI Data) 2 10548 ( 10.30kB)

Total ROM Size (Code + RO Data + RW Data) 1 25164 ( 24.57kB)

```

\_\_\_\_\_\_

#### Examine the Local Symbols section.

- 7. Which is the largest symbol of type "Thumb Code", and how large is it in bytes?

- 8. Which is the largest symbol of type "Data", and how large is it in bytes?

#### Examine the Global Symbols section.

- 9. Which is the largest symbol of type "Thumb Code", and how large is it in bytes?

- 10. Which is the largest symbol of type "Data", and how large is it in bytes?

| 4981 | 7 svcRtxThreadNew      | 0x00004821 | Thumb Code 7 484 rtx_thread.o(.text.svcRtxThreadNew)     |

|------|------------------------|------------|----------------------------------------------------------|

| 5040 | 8 os_mem               | 0x200005c8 | Data 8 4096 rtx_lib.o(.bss.os)                           |

| 5245 | 9 _dmul                | 0x000009c9 | Thumb Code 9 558 dmul.o(.text)                           |

| 5416 | 10 Lucida_Console12x19 | 0x000050e0 | Data 10 3831 lucida_12x19.o(.rodata.Lucida_Console12x19) |

Examine the **first** part of the **Image component sizes** section to determine the memory requirements of the **program** objects.

- 11. Which object member has the largest component of type "Code (inc. Data)" (first column), and how large is that component?

- 12. Which object member has the largest component of type "RO Data", and how large is that component?

- 13. Which object member has the largest component of type "RW Data", and how large is that component?

- 14. Which object member has the largest component of type "ZI Data", and how large is that component?

| Code    | (inc. data) | RO Data | RW Data | ZI Data | Debug    | Object Name               |

|---------|-------------|---------|---------|---------|----------|---------------------------|

| 456     | 76          | 0       | 1       | 36      | 5595     | adc.o                     |

| 0       | 0           | 0       | 27      | 3       | 1020     | colors.o                  |

| 1176    | 166         | 0       | 88      | 3861    | 10391    | control.o                 |

| 80      | 12          | 108     | 0       | 0       | 2061     | debug.o                   |

| 32      | 4           | 0       | 0       | 0       | 797      | delay.o                   |

| 180     | 48          | 0       | 0       | 17      | 4633     | dma.o                     |

| 476     | 110         | 36      | 10      | 4       | 7484     | fault.o                   |

| 32      | 0           | 0       | 0       | 0       | 1413     | fx.o                      |

| 542     | 0           | 0       | 0       | 0       | 5183     | <pre>lcd_graphics.o</pre> |

| 768     | 48          | 6       | 12      | 20      | 5515     | <pre>lcd_text.o</pre>     |

| 164     | 32          | 0       | 0       | 0       | 2109     | leds.o                    |

| 0       | 0           | 12 3831 | 0       | 0       | 522      | 2lucida_12x19.o           |

| 104     | 12          | 0       | 1       | 0       | 1078     | main.o                    |

| 140     | 32          | 0       | 0       | 20      | 3614     | profile.o                 |

| 0       | 0           | 36      | 0       | 4       | 728      | region.o                  |

| 4       | 0           | 0       | 0       | 0       | 714      | rtx_config.o              |

| 140     | 4           | 268     | 0       | 14 4941 | 7602     | 4rtx_lib.o                |

| 16      | 4           | 0       | 0       | 0       | 6335     | sound.o                   |

| 11 1924 | 92          | 168     | 0       | 8       | 12964    | 11st7789.o                |

| 80      | 44          | 192     | 0       | 256     | 940      | startup_mk125z4.o         |

| 224     | 44          | 0       | 4       | 0       | 3266     | system_mkl25z4.o          |

| 232     | 44          | 108     | 0       | 16      | 3491     | threads.o                 |

| 308     | 40          | 0       | 4       | 0       | 6297     | timers.o                  |

| 448     | 44          | 0       | 17      | 0       | 3411     | touchscreen.o             |

| 1116    | 96          | 9       | 13 732  | 1       | 6322     | 13ui.o                    |

|         |             |         |         | ,       | <u> </u> |                           |

Examine the **second** part of the **Image component sizes** section (with the last column **Library Member Name**) to determine the memory requirements of the **library member objects.**

- 15. Which library member has the largest component of type "Code (inc. Data)" (first column), and how large is that component?

- 16. Which library member has the largest component of type "RO Data", and how large is that component?

- 17. Which library member has the largest component of type "RW Data", and how large is that component?

- 18. Which library member has the largest component of type "ZI Data", and how large is that component?

| Code (i | nc. data) | RO Data | RW Data | ZI Data | Debug  | Library Member Name   |     |    |   |   |       |     |                       |

|---------|-----------|---------|---------|---------|--------|-----------------------|-----|----|---|---|-------|-----|-----------------------|

|         |           |         |         |         |        | -                     | 16  | 0  | 0 | 0 | 0     | 68  | exit.o                |

| 164     | 8         | 0       | 0       | 0       | 658    | irq_armv6m.o          | 6   | 0  | 0 | 0 | 0     | 136 | heapauxi.o            |

| 126     | 20        | 0       | 0       | 1       | 2812   | os_systick.o          | 0   | 0  | 0 | 0 | Ø     | 0   | indicate semi.o       |

| 132     | 8         | 0       | 0       | 0       | 2729   | rtx delay.o           | 2   | 0  | 0 | 0 | 0     | 0   | libinit.o             |

| 710     | 56        | 11      | 17 164  | 0       | 157931 | 7rtx_kernel.o         | 2   | 0  | 0 | 0 | 0     | 0   | libinit2.o            |

| 244     | 0         | 0       |         | 0       | 2665   | rtx_memory.o          | 2   | 0  | 0 | 0 | 0     | 0   | libshutdown.o         |

| 156     | 0         | 0       | 0       | 0       | 14433  | rtx_mempool.o         | 2   | 0  | 0 | 0 | 0     | 0   | libshutdown2.o        |

| 1510    | 44        | 0       | 0       | 0       | 18183  | rtx_msgqueue.o        | 8   | 4  | 0 | 0 | 18 96 | 68  | 8libspace.o           |

| 922     | 28        | 0       | 0       | 0       | 9527   | rtx_mutex.o           | 48  | 0  | 0 | 0 |       | 72  | llmul.o               |

| 364     | 18        | 0       | 0       | 0       | 4871   | rtx_system.o          | 64  | 4  | 0 | 0 | 0     | 84  | noretval2snprintf.o   |

| 15 1998 | 76        | 0       | 0       | 0       | 315961 | 5rtx_thread.o         | 40  | 4  | 0 | 0 | 0     | 84  | noretval_2sprintf.o   |

| 256     | 16        | 0       | 0       | 0       | 9965   | rtx_timer.o           | 64  | 0  | 0 | 0 | 0     | 108 | rt_memclr.o           |

| 86      | 0         | 0       | 0       | 0       | 0      | dczerorl2.o           | 186 | 0  | 0 | 0 | 0     | 144 | rt_memcpy.o           |

| 8       | 0         | 0       | 0       | 0       | 68     | main.o                | 2   | 0  | 0 | 0 | 0     | 0   | rtexit.o              |

| 392     | 6         | 1617    | 0       | 0       | 761    | 6printf_flags_ss_wp.o | 10  | 0  | 0 | 0 | 0     | 0   | rtexit2.o             |

| 14      | 0         | 0       | 0       | 0       | 60     | printf_wp.o           | 40  | 0  | 0 | 0 | 0     | 60  | rtudiv10.o            |

| 0       | 0         | 0       | 0       | 0       | 0      | rtentry.o             | 68  | 6  | 0 | 0 | 0     | 72  | strlen.o              |

| 20      | 0         | 0       | 0       | 0       | 0      | rtentry2.o            | 12  | 4  | 0 | 0 | 0     | 60  | sys_exit.o            |

| 6       | 0         | 0       | 0       | 0       | 0      | rtentry4.o            | 62  | 0  | 0 | 0 | 0     | 80  | sys_stackheap_outer.o |

| 60      | 8         | 0       | 0       | 0       | 0      | _scatter.o            | 2   | 0  | 0 | 0 | 0     | 68  | use_no_semi.o         |

| 28      | 0         | 0       | 0       | 0       | 0      | scatter_zi.o          | 46  | 0  | 0 | 0 | 0     | 60  | cmpret.o              |

| 46      | 0         | 0       | 0       | 0       | 100    | _printf_char.o        | 108 | 10 | 0 | 0 | 0     | 72  | dfixi.o               |

| 48      | 6         | 0       | 0       | 0       | 88     | _printf_char_common.o | 88  | 0  | 0 | 0 | 0     | 92  | dflti.o               |

| 10      | 0         | 0       | 0       | 0       | 0      | _printf_d.o           | 584 | 26 | 0 | 0 | 0     | 84  | dmul.o                |

| 108     | 18        | 0       | 0       | 0       | 76     | _printf_dec.o         | 348 | 8  | 0 | 0 | 0     | 160 | faddsub.o             |

| 176     | 0         | 0       | 0       | 0       | 84     | _printf_intcommon.o   | 44  | 0  | 0 | 0 | 0     | 136 | fcmp.o                |

| 78      | 0         | 0       | 0       | 0       | 100    | _printf_pad.o         | 100 | 4  | 0 | 0 | 0     | 68  | fcmpin.o              |

| 2       | 0         | 0       | 0       | 0       | 0      | _printf_percent.o     | 76  | 0  | 0 | 0 | 0     | 68  | ffixi.o               |

| 4       | 0         | 0       | 0       | 0       | 0      | _printf_percent_end.o | 48  | 0  | 0 | 0 | 0     | 60  | ffixui.o              |

| 10      | 0         | 0       | 0       | 0       | 0      | _printf_s.o           | 94  | 0  | 0 | 0 | 0     | 92  | fflti.o               |

| 82      | 0         | 0       | 0       | 0       | 72     | _printf_str.o         | 84  | 4  | 0 | 0 | 0     | 76  | fgef.o                |

| 10      | 0         | 0       | 0       | 0       | 0      | _printf_u.o           | 176 | 4  | 0 | 0 | 0     | 80  | fmul.o                |

| 16      | 0         | 0       | 0       | 0       | 60     | _snputc.o             | 16  | 6  | 0 | 0 | 0     | 68  | fnan2.o               |

| 10      | 0         | 0       | 0       | 0       | 60     | _sputc.o              | 94  | 0  | 0 | 0 | 0     | 68  | retnan.o              |

| 1006    | 4         | 0       | 0       | 0       | 184    | aeabi_sdivfast.o      | 0   | 0  | 0 | 0 | 0     | 0   | usenofp.o             |

|         |           |         |         |         |        |                       |     |    |   |   |       |     | •                     |

- Getting Started

Install Ghidra

MDK-ARM

- ▲ Memory Requirements

Linker Map File

Ghidra

- Examining Object Code and Control Flow Ignoring Control Flow Simple Control Flow Complex Control Flow

- Examining Function Calling Behavior Linker Static Call Graph Ghidra Source Code vs. Decompiled Code

In Ghidra, open the Functions window (Window -> Functions). Click on the Function Size to sort by size.

- 19. What are the name and size of the largest function?

- 20. What are the name and size of the second-largest function?

- 21. What are the name and size of the third-largest function?

- 22. Do this information match what you found above in the map file?

- 23. Does Ghidra differentiate between local and global symbols?

|    | Functions - 245 item | S        |                                 |            | <b>■</b>    <b>≥ ■</b>   × |

|----|----------------------|----------|---------------------------------|------------|----------------------------|

|    | Name                 | Location | Function Signature              | Function S | ize 🕝                      |

| 19 | _dmul                | 000009c8 | undefined _dmul()               | 1          | 9 558                      |

| 20 | LCD_Draw_Line        | 000016d0 | <pre>void LCD_Draw_Line(P</pre> | 2          | 0 542                      |

| 21 | svcRtxThreadNew      | 00004820 | osThreadId_t svcRtxT            | 2          | 1 484                      |

|    | LCD_Text_PrintChar   | 000021d0 | <pre>void LCD_Text_PrintC</pre> |            | 436                        |

|    | Control_HBLED        | 000010d8 | undefined Control_HB            |            | 428                        |

|    | svcRtxMessageQue     | 0000427c | osMessageQueueId_t s            |            | 428                        |

|    | LCD_Fill_Rectangle   | 00001a20 | void LCD_Fill_Rectan            |            | 418                        |

|    | LCD_TS_Read          | 00001f94 | uint32_t LCD_TS_Read            |            | 394                        |

- 24. What are the name (label) and size in bytes of the largest data item in memory (not in \_elf\*, .symtab, .strtab, .debug\_frame, .comment, etc.)?

- 25. What are the name (label) and size in bytes of the second-largest data item in memory (not in \_elf\*, .symtab, .strtab, .debug\_frame, .comment, etc.)?

- 26. What are the name (label) and size in bytes of the third-largest data item in memory (not in \_elf\*, .symtab, .strtab, .debug\_frame, .comment, etc.)?

- 27. Does this information match what you found above in the map file? If not, try to explain the difference.

| Defined Da | Defined Data - 3153 items |                 |                             |  |  |  |

|------------|---------------------------|-----------------|-----------------------------|--|--|--|

| Data       | Location                  | Туре            | Size                        |  |  |  |

| ??         | 200005c8                  | uint64_t[512]   | 24 4096 os_mem              |  |  |  |

| 1111       | 000050e0                  | uint8_t[3831]   | 25 3831 Lucida_Console12x19 |  |  |  |

| ??         | 1ffffe00                  | uint16_t[960]   | 1920 g_set_sample           |  |  |  |

| ??         | 1ffff600                  | uint16_t[960]   | 1920 g_meas_sample          |  |  |  |

| ??         | 20001908                  | undefined1[256] | 256 Heap_Mem                |  |  |  |

| ??         | 200017d8                  | uint64_t[32]    | 256 os_timer_thread_stack   |  |  |  |

| ??         | 200016d8                  | uint64_t[32]    | 256 os_idle_thread_stack    |  |  |  |

- Getting Started

Install Ghidra

MDK-ARM

- Memory Requirements Linker Map File Ghidra

- Examining Object Code and Control Flow

Ignoring Control Flow

Simple Control Flow

Complex Control Flow

■ Examining Function Calling Behavior

Linker Static Call Graph

Ghidra

Source Code vs. Decompiled Code

For the following questions, look in the disassembly window to see the object code which implements the function.

- 1. Which is the first instruction of the function Multiply\_FX? Include address, machine code, opcode and operand.

- 2. **ECE 561 Only:** Enter the start address of the function from the disassembly window and the start address for the function listed in the map file. Explain why they don't exactly match.

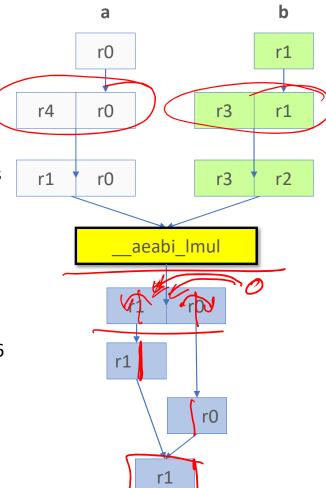

- 3. When BL.W \_\_aeabi\_lmul executes, which registers hold variable pa?

- 4. When BL.W \_\_aeabi\_lmul executes, which registers hold variable pb?

- 5. Immediately after BL.W \_\_aeabi\_lmul completes, which registers hold variable p?

- 6. Which instruction performs the return-from-subroutine? Include address, machine code, opcode and operand.

#### Arguments longer than 1 word are ordered Ignoring Control Flow Register Contents After Instruction Executes

| push | {r4,lr}    |

|------|------------|

| asrs | r4,a,#0x1f |

| asrs | r3,b,#0x1f |

| mov  | r2,b       |

| mov  | b,r4       |

| bl   | _ll_mul    |

|      |            |

| lsls | b,b,#0x10  |

| lsrs | a,a,#0x10  |

| orrs | a,b        |

| pop  | {r4,pc}    |

| r0 (                          | "a")                          | r1 ("b")                        |                               | r2 | r3            | r4                  |                                                                    |

|-------------------------------|-------------------------------|---------------------------------|-------------------------------|----|---------------|---------------------|--------------------------------------------------------------------|

|                               | a                             | ŀ                               | 0                             |    |               |                     |                                                                    |

|                               | а                             |                                 | 0                             |    |               | pa MSW              | sign extend <b>a</b> to get <b>pa</b> bits 63-32                   |

|                               | а                             |                                 | 0                             |    | pb MSW        | pa MSW              | sign extend <b>b</b> to get <b>pb</b> bits 63-32                   |

|                               | a                             | b                               |                               | b  | <b>pb</b> MSW | pa MSW              |                                                                    |

|                               | a                             | pa N                            | ЛSW                           | b  | pb MSW        | pa MSW              |                                                                    |

| p L                           | p LSW p MSW                   |                                 |                               |    |               | r0, r1 as two words |                                                                    |

| <b>p</b> 3 <sup>rd</sup> MSHW | p <b>L</b> SHW                | <b>p</b> MSHW                   | <b>p</b> 2 <sup>nd</sup> MSHW |    |               |                     | r0, r1 as four half-words                                          |

| <b>p</b> 3 <sup>rd</sup> MSHW | p LSHW                        | p 2 <sup>nd</sup> MSHW          | 0                             |    |               |                     | shift p MSW left to get lower halfword,<br>zero out upper halfword |

| 0                             | <b>p</b> 3 <sup>rd</sup> MSHW | <b>p</b> 2 <sup>nd</sup> MSHW 0 |                               |    |               |                     | shift p LSW right to get upper halfword, zero out lower halfword   |

| p 2 <sup>nd</sup> MSHW        | <b>p</b> 3 <sup>rd</sup> MSHW | <b>p</b> 2 <sup>nd</sup> MSHW 0 |                               |    |               |                     | OR together results to get middle 32 bits of <b>p</b>              |

#### Signed 16.16 \* 16.16 Explained

PUSH {r4,lr}

ASRS r4,r0,#31

ASRS r3,r1,#31

MOV r2, r1 MOV r1, r4

BL \_\_aeabi\_lmul

LSLS r1, r1, #16 LSRS r0, r0, #16 ORRS r0, r0, r1

**POP** {r4,pc}

- Sign-extension to 64 bits

- a (r0) and b (r1) to 64 bits pa (r4:r0) and pb (r3:r2)

- ASRS: arithmetic shift right performs sign extension by setting all of upper word's sign bits to match lower word's sign

- Move pa and pb into argument registers (r1:r0 and r3:r2)

- Call \_\_aeabi\_lmul for long multiply

- Extract middle 32 bits of result

- LSLS: logical shift left extracts lower 16 bits of r1

- LSRS: logical shift right extracts upper 16 bits of r0

- ORRS: merges together middle 32 bits

- Getting Started

Install Ghidra

MDK-ARM

- Memory Requirements Linker Map File Ghidra

- Examining Object Code and Control Flow Ignoring Control Flow

Simple Control Flow

Complex Control Flow

▲ Examining Function Calling Behavior

Linker Static Call Graph

Ghidra

Source Code vs. Decompiled Code

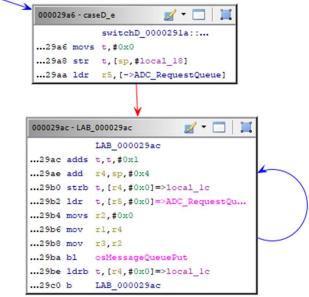

# Simple Control Flow #7 (v1.0): CFG of Fault Fill Queue

- 2 or 3 basic blocks ok since bl osMessageQueuePut may be interpreted as ending basic block

- Note that there should not be a basic block for the subroutine osMessageQueuePut. The call instruction (BL) is in the 2<sup>nd</sup> basic block.

| BBs | no | yes-<br>branch | yes-<br>call | yes-<br>return |

|-----|----|----------------|--------------|----------------|

| 3   | 1  | 1              | 1            | 0              |

| 2   | 1  | 1              | 0            | 0              |

# Simple Control Flow #8 (v1.0): CFG of Fault Fill Queue

- 2 or 3 basic blocks ok since bl osMessageQueuePut may be interpreted as ending basic block

- Addresses should match basic blocks listed in #7, not necessarily what's in this diagram.

- Labeled edges connecting basic blocks as shown

- Note that there should not be a basic block for the subroutine osMessageQueuePut. The call instruction (BL) is in the 2<sup>nd</sup> basic block.

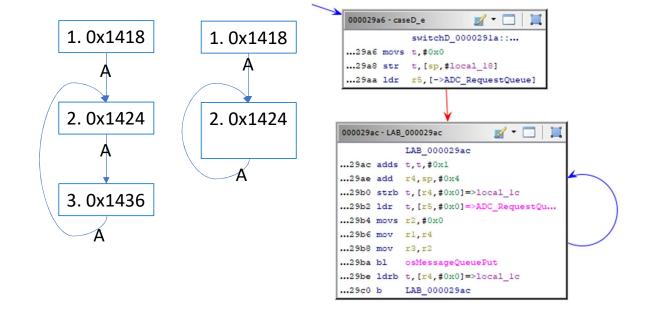

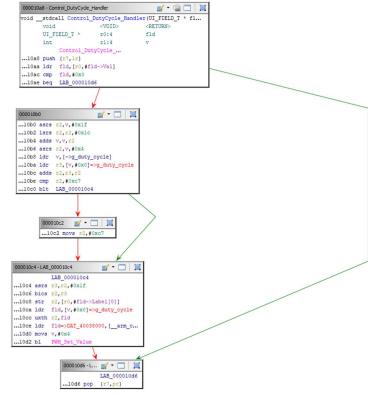

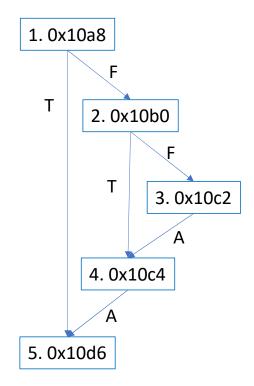

Simple Control Flow #7 (v1.1+): CFG of Control DutyCycle Handler

| BBs | no | yes-<br>branch | yes-<br>call | yes-<br>return |

|-----|----|----------------|--------------|----------------|

| 5   | 2  | 2              | 0            | 1              |

| 5   | 1  | 2              | 1            | 1              |

Note that there should not be a basic block for the subroutine PWM\_Set\_Value. The call instruction (BL) is in the 4<sup>th</sup> basic block.

# Simple Control Flow #8 (v1.1+): CFG of Control\_DutyCycle\_Handler

- 5 basic blocks, labeled as shown

- Addresses should match basic blocks listed in #7, not necessarily what's in this diagram.

- Labeled edges connecting basic blocks as shown

- Note that there should not be a basic block for the subroutine PWM\_Set\_Value. The call instruction (BL) is in the 4<sup>th</sup> basic block.

- Getting Started

Install Ghidra

MDK-ARM

- Memory Requirements Linker Map File Ghidra

- Examining Object Code and Control Flow Ignoring Control Flow Simple Control Flow Complex Control Flow

- Examining Function Calling Behavior Linker Static Call Graph Ghidra Source Code vs. Decompiled Code

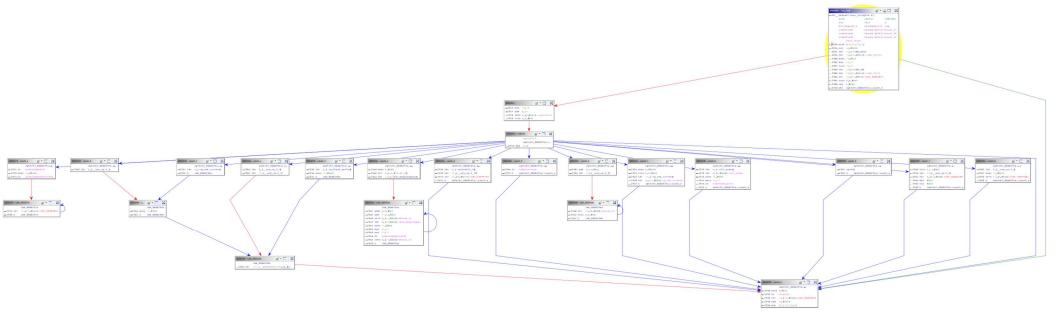

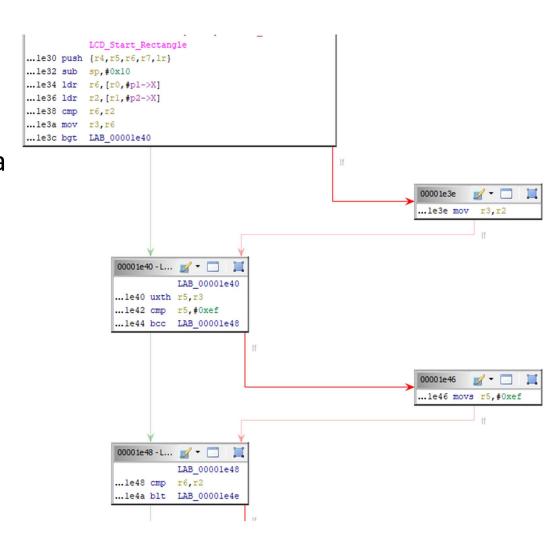

- Should show the right function (LCD\_Start\_Rectangle) using this layout

- Text doesn't have to be legible, but basic blocks and control flow edges must be visible

- Must be from Ghidra for Test\_Fault

- May be a different layout from this one

- Must show basic blocks and edges

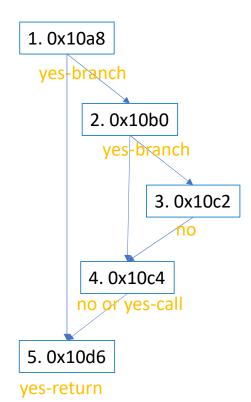

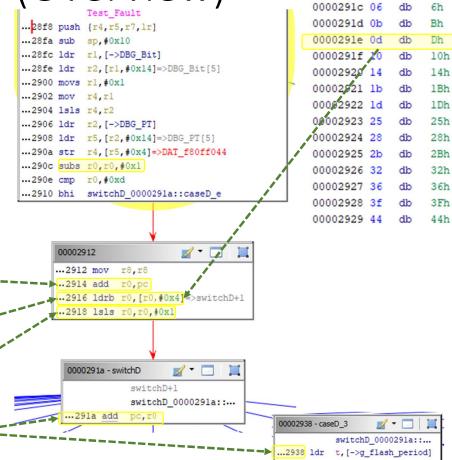

Complex Control Flow #15 (Overview)

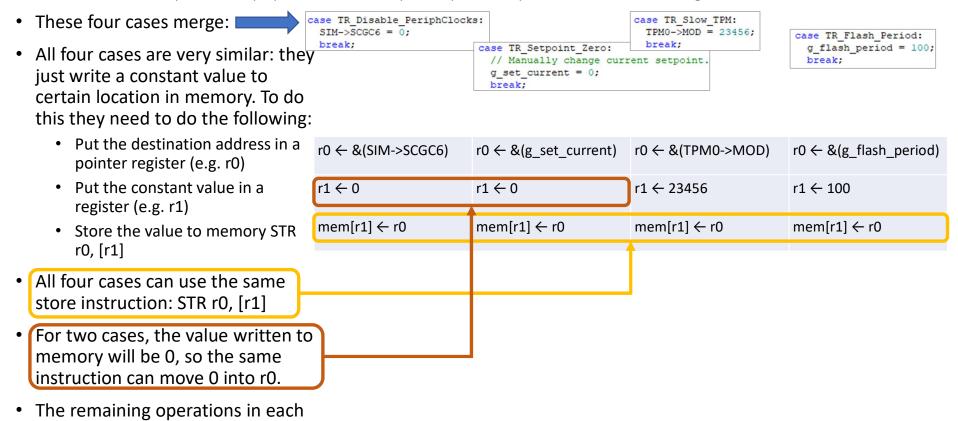

- Test case number t (in r0) is decremented by one, since table has covers cases 1 through 14. Example: t = 3, so r0 <- 3-1 = 2</li>

- r0 is compared to the largest test case offset 0xd (14–1=13), and the result determines if bhi branches.

- r0 > 13?

- branch to caseD\_e, which is code following last case statement, since there is no default case

- r0 <= 13? Ex: r0 = 2 <= 13

- Note: pc is address of cur. instruction + 4. Arm Arch. Ref. Manual, DDI 0419C

Read the PC value, that is, the address of the current instruction +4.

- Add pc to r0, so r0 points to .... Ex: r0 <- 2 + (0x2914 + 4) = 0x2918 + 2 = 0x291a</li>

- Load register r0 with byte from entry in jump table (in memory at address r0+4). Ex: r0 <- memory[0x291a+4] = memory[0x291e] = 0xd = 13

- Shift r0 left by one bit (multiply by two) to convert offset to bytes. Ex: r0 <- 26</li>

- Add r0 to pc, causing the program to jump to that case's code. Ex: pc <- (0x291a + 4) + 26 = 0x291e + 26 = 0x2938</li>

..293c b

LAB 0000298e

Jump Table

Address

```

switch (t) {

case TR None:

switchD_0000291a::caseD_1

break;

Complex Control

0000292a 7d 20

movs

r0,#0x7d

case TR Setpoint High:

0000292c c0 00

1818

r0, r0, #0x3

// Manually change current setpo

ldr

rl, [->g set current]

g_set_current = 1000;

00002930 08 60

r0, [r1, #0x0]=>g_set_current

00002932 2d e0

switchD 0000291a::caseD e

// Manually change current setpoin Flow #15 (Details)

case TR Setpoint Zero:

switchD 0000291a::caseD 2

00002934 2e 48

r0, [->g_set_current]

switchD_0000291a::caseD_a

break;

00002974 01 f0 92 10 b1

00002936 18 e0

LAB 0000296a

osThreadGetId

case TR Flash Period:

00002978 30 21

r1.#0x30

g_flash_period = 100;

0000297a 01 f0 b5 fa

osThreadSetPriority

break;

00002938 2c 48

3 ldr

r0, [->g_flash_period]

case TR_PID_FX_Gains:

00000293a 64 21

rl.#0x64

0x291a + 4 + 2*0xD

// Corrupt one of the compensator gains

0000297e ec 60

r4, [r5, #0xc]=>DAT_f80ff04c

str

LAB 0000298e

0000293c 27 e0

00002980 fd e7

plantPID TX.iGain = -1000;

LAB 0000297e

break;

= 0x2938

switchD 0000291a::caseD 4

switchD_0000291a::caseD_b

case TR LCD mutex.

0000293e 29 48

ldr

r0, [->plantPID_FX]

00002982 13 48

// Take LCD mutex, don't return it

r0, [_arm_cp.2_5]

00002940 29 49

ldr

rl, [_arm_cp.2_11]

00002984 18 21

r1, #0x18

osMutexAcquire(LCD_mutex, osWaitForever);

00002942 41 61

rl,[r0,#0x14]=>DAT_lfffff418

00002986 01 70

rl,[r0,#0x0]=>DAT 40064004

strb

00002944 24 e0

switchD 0000291a::caseD e

switchD 000029la::switchda

00002988 02 e0

switchD 000029la::caseD e

case TR Fill Queue:

// Fill ADC request queue with warbage

switchD_000029la::caseD_c

switchD 0000291a::caseD 5

0000291c 06

db

6h

0000298a Of 48

r0, [_arm_cp.2_3]

Fault Fill Queue();

00002946 26 48

ldr

r0, [->LCD_mutex]

0000298c Of 49

rl, [ arm cp.2 4]

00002948 00 68

ldr

r0, [r0, #0x0] => LCD mutex

0000291d 0b

Bh

case TR Disable PeriphClocks:

0000294a 00 21

rl, #0x0

movs

LAB_0000298e

SIM->SCGC6 = 0;

0000294c c9 43

mvns

rl.rl

0000298e 01 60

rl=>s__000050e0+2752,[r0,#0x0]=

0000291e 0d

0000294e 00 f0 b7 fd

osMutexAcquire

case TR Disable All IRQs:

00002952 1d e0

switchD_000029la::caseD_e

switchD 000029la::caseD e

// Disable Interrupts

0000291f 10

10h

15 No code for these cases

switchD_000029la::caseD_6

disable irq();

00002954 72 b6

00002920 14

14h

Code after switch (t) { ... }

00002956 lb e0

switchD_000029la::caseD_e

case TR Disable ADC IRQ:

// Disable ADC interrupt

00002921 lb

switchD_0000291a::caseD_7

NVIC DisableIRQ(ADC0 IRQn);

0002996 ac 60

r4, [r5, #0x8]=>DAT f80ff048

str

00002958 c8 03

lsls

ro, rl, #0xf

break:

0002998 04 b0

add

sp. #0x10

0000295a le 49

ldr

rl, [_arm_cp.2_6]

00002922 ld

case TR osKernelLock:

1Dh

000299a b0 bd

pop

00002950 08 60

r0,[r1,#0x0]=>DAT e000e180

// Lock kernel - don't let other tasks run

0000295e bf f3 4f 8f

// See details at https://www.keil.com/pac

switchD_000029la::caseD_d

00002923 25

25h

00002962 bf f3 6f 8f

#0xf

0000299c 03 a8

r0, sp, #0xc

3 add

osKernelLock();

00002966 13 e0

switchD_000029la::caseD_e

0000299e 09 49

rl, [_arm_cp.2_2]

00002924 28

28h

case TR Change MCU Clock:

switchD 0000291a::caseD 8

LAB 000029a0

// Change MCU clock frequency

000029a0 01 60

rl,[r0,#0x0]=>local_14

00002925 2b

00002968 1b 48

r0, [ arm cp.2 7]

MCG->C5 = 0x0018;

000029a2 00 1f

break:

000029a4 fc e7

LAB_000029a0

LAB_0000296a

00002926 32

case TR Slow TPM:

0000296a 00 21

r1, #0x0

TPM0->MOD = 23456;

switchD 0000291a::caseD e

0000296c Of e0

LAB_0000298e

00002986 00 20

00002927 36

36h

14 str

000029a8 02 90

r0, [sp, #local_18]

case TR Stack Overflow:

switchD 0000291a::caseD 9

000029aa 0c 4d

r5, [->ADC RequestQueue]

ldr

n = Overflow Stack();

00002928 3f

3Fh

0000296e 00 f0 fd

00002972 Od e0

switchD 0000291a::caseD e

LAB 000029ac

case TR High Priority Thread:

000029ac 40 1c

r0.r0.#0x1

adds

13 00002929 44

44h

// Raise own priority very high, then go i

000029ae 01 ac

r4, sp, #0x4

osThreadSetPriority(osThreadGetId(), osPri

000029b0 20 70

r0, [r4, #0x0] => local_lc

000029b2 28 68

r0, [r5, #0x0] => ADC RequestQueue

while (1)

00002964 00 22

r2, #0x0

DEBUG TOGGLE (DBG FAULT POS);

movs

000029b6 21 46

mov

rl.r4

break:

00002968 13 46

case TR End:

000029ba 00 f0 47 fd

b1

osMessageQueuePut

break;

000029be 20 78

r0, [r4, #0x0] => local_lc

000029c0 f4 e7

LAB 000029ac

```

ECE 561 only: If the number of test cases don't match, try to explain why.

- Test cases TR\_None (0) and TR\_End (15) both do nothing, so there is no case code generated for them.

- Before the jump table, those cases are detected with one test

- They are both handled by this code:

- Subtract 1 from r0

- 0 -> 0xfffffff

- 15 -> 14 (0x000000e)

- Compare with 0xd (13)

```

...290c subs r0,r0,#0x1

...290e cmp r0,#0xd

...2910 bhi switchD_0000291a::caseD_e

```

- bhi: Branch if unsigned greater than is true

- Both are higher than 0xd, so branch to caseD\_e, which is code which follows the switch statement

```

switch (t) {

case TR None:

break;

case TR Setpoint High:

// Manually change current setpoint.

g_set_current = 1000;

break:

case TR Setpoint Zero:

// Manually change current setpoint.

g_set_current = 0;

break:

case TR Flash Period:

g flash period = 100;

break;

case TR PID FX Gains:

// Corrupt one of the compensator gains

plantPID_FX.iGain = -1000;

break:

case TR LCD mutex:

// Take LCD mutex, don't return it

osMutexAcquire(LCD mutex, osWaitForever);

case TR Fill Queue:

// Fill ADC request queue with garbage

Fault_Fill_Queue();

break;

case TR Disable PeriphClocks:

SIM->SCGC6 = 0;

break:

case TR_Disable_All_IRQs:

// Disable Interrupts

disable_irq();

case TR Disable ADC IRQ:

// Disable ADC interrupt

NVIC_DisableIRQ(ADCO_IRQn);

break:

case TR osKernelLock:

// Lock kernel - don't let other tasks run

// See details at https://www.keil.com/pac

osKernelLock();

case TR Change MCU Clock:

// Change MCU clock frequency

MCG->C5 = 0x0018;

break:

case TR Slow TPM:

TPMO->MOD = 23456;

break:

case TR_Stack_Overflow:

n = Overflow Stack();

case TR High Priority Thread:

// Raise own priority very high, then go

osThreadSetPriority(osThreadGetId(), osPri

DEBUG TOGGLE (DBG FAULT POS);

break:

case TR End:

break;

```

ECE 561 only: If the number of test cases ending in infinite loops don't match, try to explain what happened.

- In source code

- one case ends in explicit infinite loop: high priority thread (10)

- Two cases call subroutine with infinite loop: stack overflow (13), fill queue (14)

- CFG shows three cases ending in infinite loops, partially matching source code.

- In cases for stack overflow (13/d), fill queue (14/3), compiler in-lined calls to subroutines with infinite loops

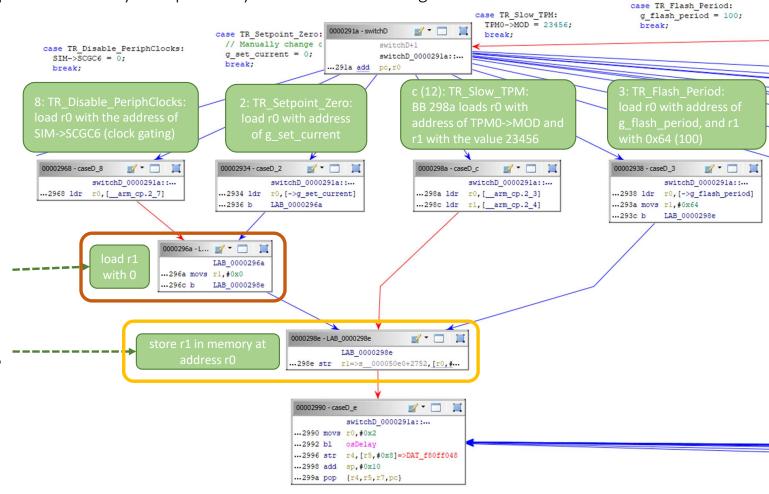

#### Complex Control Flow #21 (1 of 2)

case different and get their own

code.

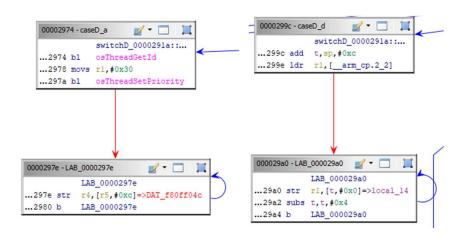

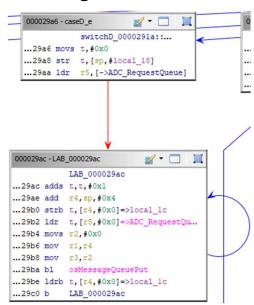

The control flow for four different cases merges into a single basic block before reaching the basic block with the call to osDelay and the pop instruction. Try to explain why the control flow merges for those cases.

#### Complex Control Flow #21 (2 of 2)

The control flow for four different cases merges into a single basic block before reaching the basic block with the call to osDelay and the pop instruction. Try to explain why the control flow merges for those cases.

- Each of the four cases gets its own code to load noncommon values

- For cases 8 and 2, the value written to memory will be 0.

The common code to load r0 with 0 is placed in BB 296a

- An instruction to store r1 to memory at [r0] is placed in BB 298e for use by all four cases.

Do all the cases end in an infinite loop or a control flow edge to another basic block? If not, which one doesn't, and why not?

- With my code, all cases end in an infinite loop or a control flow edge to another block.

- It's possible that if the compiler didn't inline a call to a function with an infinite loop (stack overflow (13/d), fill queue (14/e)), then the basic block would just end in a subroutine call (BL, BLX instruction) with no successor BB.

Getting Started

Install Ghidra

MDK-ARM

Memory Requirements

Linker Map File

Ghidra

Examining Object Code and Control Flow

Ignoring Control Flow

Simple Control Flow

Complex Control Flow

■ Examining Function Calling Behavior

Linker Static Call Graph

Ghidra

Source Code vs. Decompiled Code

Getting Started

Install Ghidra

MDK-ARM

Memory Requirements Linker Map File Ghidra

- Examining Object Code and Control Flow Ignoring Control Flow Simple Control Flow Complex Control Flow

- Examining Function Calling Behavior

Linker Static Call Graph

Ghidra

Source Code vs. Decompiled Code

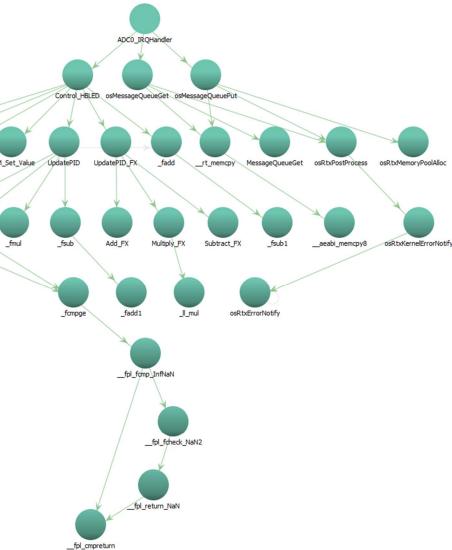

Examining Function Calling Behavior #10

20%: Root node must be ADC0\_IRQHandler

• 30%: All direct calls must be included (scale proportionally for missing or extra function nodes)

50%: All indirect calls must be included (scale proportionally for missing or extra function nodes)

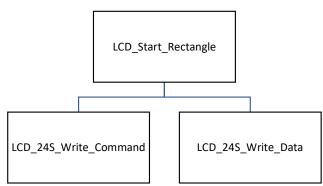

#### Examining Function Calling Behavior #11

Use Ghidra to create a function call graph for LCD\_Start\_Rectangle. Compare it with what you would expect from the source code (located in ST7789.c). What are the differences? How do you explain them?

#### • Differences:

The source code has multiple subroutine calls to LCD\_24S\_Write\_Command and LCD\_24S\_Write\_Data

The Ghidra function call graph has no subroutine calls.

Explanation: The compiler in-lined the function calls when optimizing the code (to speed it up).

#### Source Code vs. Decompiled Code #1

```

uint32 t LCD Start Rectangle (PT T * p1, PT T * p2) {

uint32 t n;

uint16 t c min, c max, r min, r max;

// Find bounds of rectangle

c min = MIN(p1->X, p2->X);

c max = MAX(p1->X, p2->X);

r min = MIN(p1->Y, p2->Y);

r max = MAX(p1->Y, p2->Y);

// Clip to display size

c max = MIN(c max, LCD WIDTH-1);

r max = MIN(r max, LCD HEIGHT-1);

n = (c max - c min + 1)*(r max - r min + 1);

if (n > 0) {

// Enable access to full screen, reset write pointer to origin

LCD 24S Write Command(0x002A); //column address set

LCD 24S Write Data(c min >> 8);

LCD 24S Write Data(c min & 0xff); //start

LCD 24S Write Data(c max >> 8);

LCD 24S Write Data(c max & 0xff); //end

LCD 24S Write Command(0x002B); //page address set

LCD 24S Write Data(r min >> 8);

LCD 24S Write Data(r min & 0xff); //start

LCD 24S Write Data(r max >> 8);

LCD 24S Write Data(r max & 0xff); //end

// Memory Write 0x2c

LCD 24S Write Command(0x002c);

return n;

```

- Getting Started

Install Ghidra

MDK-ARM

- Memory Requirements

Linker Map File

Ghidra

- Examining Object Code and Control Flow Ignoring Control Flow Simple Control Flow Complex Control Flow

- Examining Function Calling Behavior

Linker Static Call Graph

Ghidra

Source Code vs. Decompiled Code

### Source Code vs. Decompiled Code #2 (option 1)

- Either option 1 or 2 (next page) is fine

- In Code Browser, Edit -> Tool Options-> Decompiler-> Analysis

Respect readonly flags

```

int32 t LCD Start Rectangle (PT T *pl, PT T *p2)

uint32 t uVarl;

uint uVar2;

uint uVar3;

uint uVar4;

ushort uVar5;

uint uVar6;

uint uVar7;

uint uVar8:

uVar8 = p1->X;

uVar3 = p2->X;

uVar5 = (ushort)uVar8;

if ((int)uVar8 <= (int)uVar3) {

uVar5 = (ushort)uVar3;

uVar7 = (uint)uVar5;

if (0xee < uVar7) {

uVar7 = 0xef;

if ((int)uVar3 <= (int)uVar8) {

uVar8 = uVar3;

uVar6 = pl->Y;

uVar4 = p2->Y;

uVar3 = uVar6;

if ((int)uVar6 <= (int)uVar4) {

uVar3 = uVar4;

uVar2 = uVar3 & 0xffff;

if (0x13e < (uVar3 & 0xffff)) {

uVar2 = 0x13f;

if ((int)uVar4 <= (int)uVar6) {

uVar6 = uVar4;

uVarl = ((uVar2 - (uVar6 & 0xffff)) + 1) * ((uVar7 - (uVar8 & 0xffff)) + 1);

if (uVarl != 0) {

_DAT_f80ff080 = _DAT_f80ff080 & 0xfffff807 | (uVar7 & 0x1fffff00) << 3 | 0x160;

DAT f80ff088 = 0x2000;

DAT f80ff084 = 0x1000;

return uVarl;

```

#### Source Code vs. Decompiled Code #2 (option 2)

In Code Browser, Edit -> **Tool Options->** Decompiler-> Analysis

Respect readonly flags

```

puVarl[1] = 0x1000;

*puVarl = *puVarl & arm cp.11 1;

2 uint32 t LCD_Start_Rectangle(PT_T *pl,PT_T *p2)

*puVarl = *puVarl | uVar9 >> 5 & 0x7f8;

puVar1[2] = 0x2000;

puVar1[1] = 0x2000;

uint *puVarl;

*puVarl = *puVarl & arm cp.11 1;

uint32 t uVar2;

*puVarl = *puVarl | (uVar9 << 0x18) >> 0x15;

uint uVar3;

puVarl[2] = 0x2000;

uint uVar4;

puVar1[1] = 0x2000;

uint uVar5;

uVar9 = arm cp.11 1;

ushort uVar6:

*puVarl = *puVarl & __arm_cp.11_1;

uint uVar7;

*puVarl = *puVarl;

uint uVar8;

puVar1[2] = 0x2000;

uint uVar9:

puVar1[1] = 0x2000;

*puVarl = *puVarl & uVar9;

puVarl = arm cp.11 0;

*puVarl = *puVarl | uVar8 << 3;

uVar9 = pl->X;

puVar1[2] = 0x2000;

uVar4 = p2->X;

puVar1[1] = 0x2000;

uVar6 = (ushort)uVar9;

puVar1[2] = 0x1000;

if ((int)uVar9 <= (int)uVar4) {

*puVarl = *puVarl & uVar9;

uVar6 = (ushort)uVar4;

*puVarl = *puVarl | 0x158;

21

puVar1[2] = 0x2000;

uVar8 = (uint)uVar6;

puVar1[1] = 0x2000;

if (0xee < uVar8) {

puVar1[1] = 0x1000;

uVar8 = 0xef:

*puVarl = *puVarl & uVar9;

25

*puVarl = *puVarl | uVar7 >> 5 & 0x7f8;

if ((int)uVar4 <= (int)uVar9) {

puVarl[2] = 0x2000;

uVar9 = uVar4:

puVar1[1] = 0x2000;

*puVarl = *puVarl & uVar9;

uVar7 = pl->Y;

*puVarl = *puVarl | (uVar7 << 0x18) >> 0x15;

uVar5 = p2->Y;

puVar1[2] = 0x2000;

uVar4 = uVar7;

puVar1[1] = 0x2000;

if ((int)uVar7 <= (int)uVar5) {

*puVarl = *puVarl & uVar9;

uVar4 = uVar5;

*puVarl = *puVarl | uVar3 >> 5 & 8;

34

puVar1[2] = 0x2000;

uVar3 = uVar4 & 0xffff;

puVar1[1] = 0x2000;

if (0x13e < (uVar4 & 0xffff)) {

*puVarl = *puVarl & uVar9;

uVar3 = 0x13f:

*puVarl = *puVarl | (uVar3 << 0x18) >> 0x15;

38

puVar1[2] = 0x2000;

if ((int)uVar5 <= (int)uVar7) {

puVarl[1] = 0x2000;

uVar7 = uVar5:

puVar1[2] = 0x1000;

*puVarl = *puVarl & uVar9;

uVar2 = ((uVar3 - (uVar7 & 0xffff)) + 1) * ((uVar8 - (uVar9 & 0xffff)) + 1);

*puVarl = *puVarl | 0x160;

if (uVar2 != 0) {

puVar1[2] = 0x2000;

arm cp.11 0[2] = 0x1000;

puVar1[1] = 0x2000;

*puVarl = *puVarl & arm cp.11 1;

puVar1[1] = 0x1000;

*puVarl = *puVarl | 0x150;

puVar1[2] = 0x2000;

return uVar2;

puVar1[1] = 0x2000;

```

### Source Code vs. Decompiled Code #3

Each MIN or MAX macro has become a compare instruction, a conditional branch, and a move instruction.

# Source Code vs. Decompiled Code #4 (option 1)

These are addresses that correspond to the fast GPIO registers for FGPIOC (Chapter 41 of KL25 SF Reference Manual, Rev. 3)

```

uVarl = ((uVar2 - (uVar6 & 0xffff)) + 1) * ((uVar7 - (uVar8 & 0xffff)) + 1);

if (uVarl != 0) {

_DAT_f80ff080 = _DAT_f80ff080 & 0xfffff807 | (uVar7 & 0xlfffff00) << 3 | 0x160;

_DAT_f80ff088 = 0x2000;

_DAT_f80ff084 = 0x1000;

}

return uVarl;

```

| F80F_F080 | Port Data Output Register (FGPIOC_PDOR)  |

|-----------|------------------------------------------|

| F80F_F084 | Port Set Output Register (FGPIOC_PSOR)   |

| F80F_F088 | Port Clear Output Register (FGPIOC_PCOR) |

#### Source Code vs. Decompiled Code #5, #6

5. One cast does appear, performing an unsigned extension of a halfword from r3 into a full word in r5

6. Most of the casts don't appear in the object code – for example a conditional branch is highlighted as implementing the code. The casts are probably in the source code to clarify how the comparisons are performed.

#### Source Code vs. Decompiled Code #7, #8

- 7. The compiler inlined the function calls. This makes the program faster.

- 8a. Without **Respect readonly flags** checked, the decompiler omits all but the last writes to \_DAT\_f80ff080, \_DAT\_f80ff088, and \_DAT\_f80ff084 because it didn't know they were control registers (not regular memory), so each write matters.

- 8b. With **Respect readonly flags** checked, the decompiler includes all writes to those addresses.

```

Respect readonly flags

uVar1 = ((uVar2 - (uVar6 & 0xffff)) + 1) * ((uVar7 - (uVar8 & 0xffff)) + 1);

if (uVarl != 0) {

DAT f80ff080 = DAT f80ff080 & 0xfffff807 | (uVar7 & 0xlfffff00) << 3 | 0xl60;

DAT f80ff088 = 0x2000;

DAT f80ff084 = 0x1000;

return uVarl;

Respect readonly flags

puVarl[1] = 0x2000;

*puVarl = *puVarl & uVar9;

*puVarl = *puVarl | uVar3 >> 5 & 8;

puVar1[2] = 0x2000;

puVar1[1] = 0x2000;

*puVarl = *puVarl & uVar9;

*puVarl = *puVarl | (uVar3 << 0x18) >> 0x15;

puVar1[2] = 0x2000;

puVar1[1] = 0x2000;

puVar1[2] = 0x1000;

*puVarl = *puVarl & uVar9;

*puVarl = *puVarl | 0x160;

puVar1[2] = 0x2000;

puVarl[1] = 0x2000;

puVar1[1] = 0x1000;

return uVar2;

```